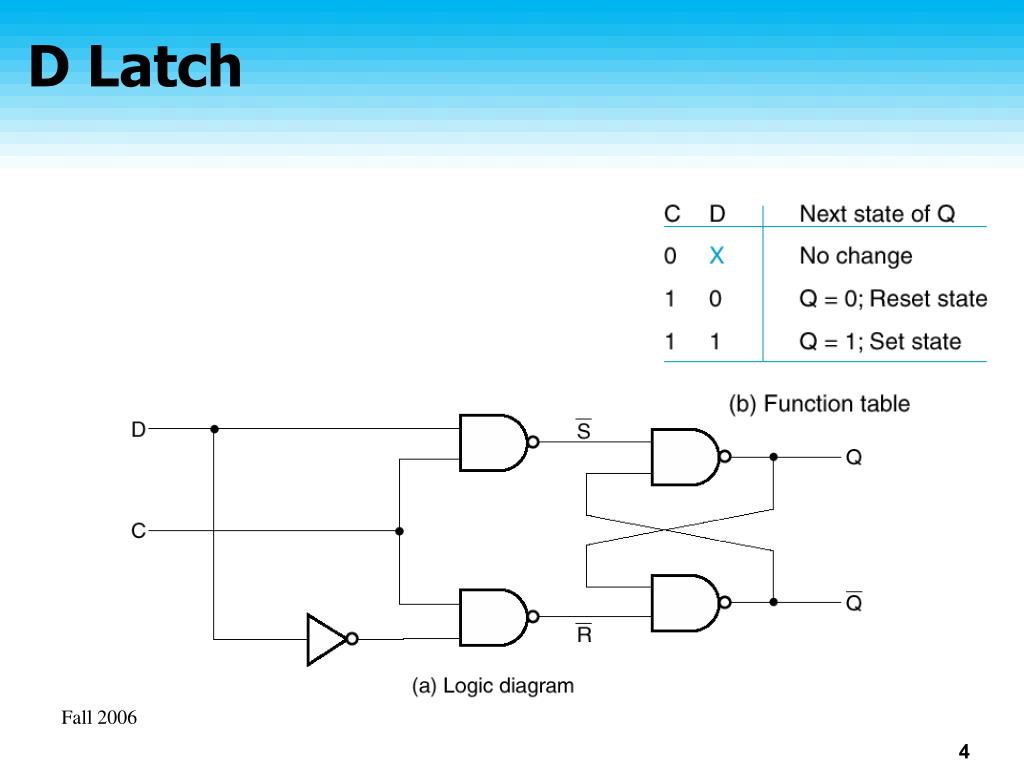

Keywords Flip-Flop, Pulse Triggered, Low Powerįlip-flops (FFS) are the fundamental storage parts used extensively altogether sorts of digital styles. Simulation is performed for various pulse triggered flip-flop to demonstrate the effectiveness of our proposed system using Micro wind 120-nm technology, analysis of power reduction is simulated by using micro wind tool.

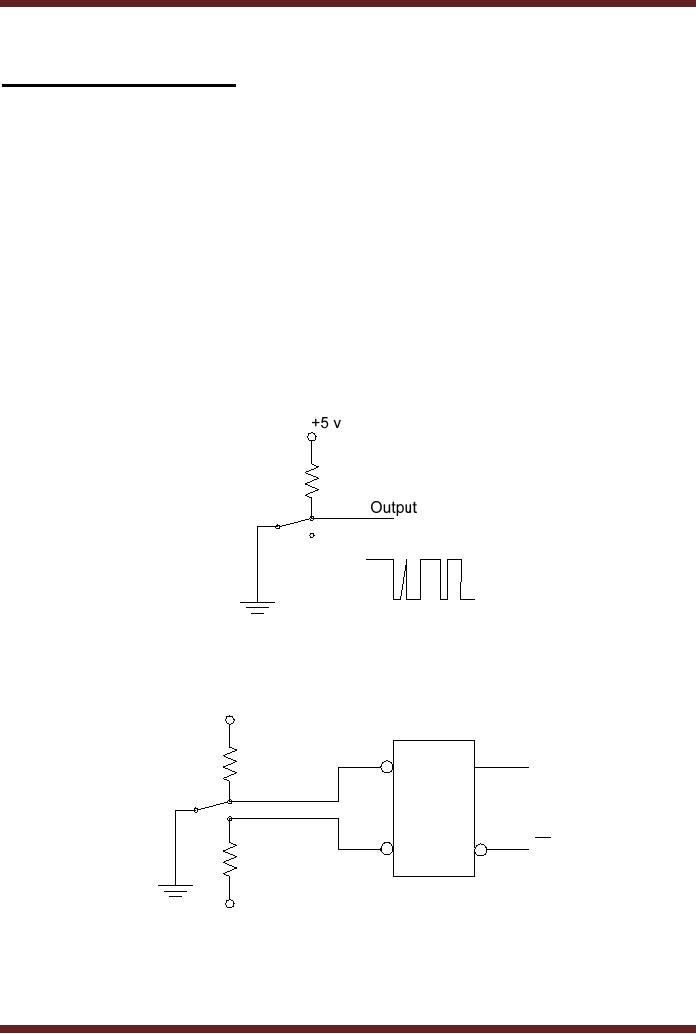

The transistor sizes of the delay inverter and pulse generation circuit are reduced for power saving. Pass-transistor logic based NAND gate is designed for pulse generation which reduces circuit complexity and enhances for faster discharge. The proposed method is pulse-triggered flip-flop (PT-FF) design based on a signal feed through scheme.

TRP Engineering College (SRM GROUP), Tiruchirappalli – 621 105, IndiaĪbstract The flip-flop is the one of the major component in VLSI low power circuits. International Journal of Engineering Research & Technology (IJERT) Low Power Pulse Triggered Flip-Flop using Signal Feed- Through Scheme

0 kommentar(er)

0 kommentar(er)